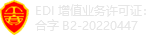

PCB布線時,有哪些技巧可以優化電磁兼容性

15

15

拍明芯城

拍明芯城

在PCB布線時,優化電磁兼容性(EMC)是至關重要的。以下是一些關鍵的技巧,可以幫助設計師提升PCB的電磁兼容性:

一、選擇合理的導線寬度

瞬變電流在印制線條上產生的沖擊干擾主要由印制導線的電感成分造成,因此應盡量減小印制導線的電感量。

印制導線的電感量與其長度成正比,與其寬度成反比,所以短而精的導線有利于抑制干擾。

對于分立元件電路,印制導線寬度在1.5mm左右通常可滿足要求;對于集成電路,印制導線寬度可在0.2~1.0mm之間選擇。

二、采用正確的布線策略

采用平等走線可以減少導線電感,但會增加導線之間的互感和分布電容。如果布局允許,最好采用井字形網狀布線結構,即一面橫向布線,另一面縱向布線,然后在交叉孔處用金屬化孔相連。

避免長距離的平等走線,以抑制印制電路板導線之間的串擾。盡可能拉開線與線之間的距離,信號線與地線及電源線盡可能不交叉。

在一些對干擾十分敏感的信號線之間設置一根接地的印制線,可以有效地抑制串擾。

三、優化高頻信號布線

高頻信號通過印制導線時容易產生電磁輻射,因此應注意以下幾點:

盡量減少印制導線的不連續性,例如導線寬度不要突變,導線的拐角應大于90度(最好采用兩個45度角),禁止環狀走線等。

時鐘信號引線最容易產生電磁輻射干擾,走線時應與地線回路相靠近,驅動器應緊挨著連接器。

總線驅動器應緊挨其欲驅動的總線。

數據總線的布線應每兩根信號線之間夾一根信號地線。

四、使用終端匹配

為了抑制出現在印制線條終端的反射干擾,除了特殊需要之外,應盡可能縮短印制線的長度和采用慢速電路。

必要時可加終端匹配,即在傳輸線的末端對地和電源端各加接一個相同阻值的匹配電阻。匹配電阻的阻值應根據集成電路的輸出驅動電流及吸收電流的最大值來決定。

五、差分信號布線

布線非常靠近的差分信號對相互之間會緊密耦合,這種耦合會減小EMI發射。

差分信號也是高速信號,所以高速設計規則通常都適用于差分信號的布線。

差分PCB線通常總是成對布線,而且它們之間的距離沿線對的方向在任意位置都保持為一個常數不變。

六、接地與分隔

將PCB接地是降低EMI的一個重要途徑。設計時應使PCB電路板總面積內的接地面積盡可能大,以減少發射、串擾和噪聲。

將模擬電路和數字電路分開,因為模擬電路的安培數較高或電流較大,應遠離高速走線或開關信號。如果可能的話,應使用接地信號保護它們。

在多層PCB上,模擬走線的布線應在一個接地層上,而開關走線或高速走線應在另一個接地層。

七、去耦電容的使用

去耦電容可減少串擾的不良影響,它們應位于設備的電源引腳和接地引腳之間,這樣可以確保交流阻抗較低,減少噪聲和串擾。

為了在寬頻率范圍內實現低阻抗,應使用多個去耦電容。

電容值最小的電容器要盡可能靠近設備,以減少對走線產生電感影響。

八、避免直角和過孔問題

應避免走線、過孔及其它元器件形成90°角,因為直角會產生輻射。在該角處電容會增加,特性阻抗也會發生變化,導致反射,繼而引起EMI。

在幾乎所有PCB布局中,都必須使用過孔在不同層之間提供導電連接。但過孔會產生電感和電容,并增加走線長度,需要進行匹配。

九、電纜和物理屏蔽

承載數字電路和模擬電流的電纜會產生寄生電容和電感,引起很多EMC相關問題。如果使用雙絞線電纜,則會保持較低的耦合水平,消除產生的磁場。

對于高頻信號,必須使用屏蔽電纜,其正面和背面均接地,以消除EMI干擾。

物理屏蔽是用金屬封裝包住整個或部分系統,防止EMI進入PCB電路。

綜上所述,通過遵循這些技巧,設計師可以顯著提升PCB的電磁兼容性,從而確保電子設備的穩定性和可靠性。

責任編輯:Pan

【免責聲明】

1、本文內容、數據、圖表等來源于網絡引用或其他公開資料,版權歸屬原作者、原發表出處。若版權所有方對本文的引用持有異議,請聯系拍明芯城(marketing@iczoom.com),本方將及時處理。

2、本文的引用僅供讀者交流學習使用,不涉及商業目的。

3、本文內容僅代表作者觀點,拍明芯城不對內容的準確性、可靠性或完整性提供明示或暗示的保證。讀者閱讀本文后做出的決定或行為,是基于自主意愿和獨立判斷做出的,請讀者明確相關結果。

4、如需轉載本方擁有版權的文章,請聯系拍明芯城(marketing@iczoom.com)注明“轉載原因”。未經允許私自轉載拍明芯城將保留追究其法律責任的權利。

拍明芯城擁有對此聲明的最終解釋權。

產品分類

產品分類

2012- 2022 拍明芯城ICZOOM.com 版權所有 客服熱線:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版權所有 客服熱線:400-693-8369 (9:00-18:00)