第一章:緒論

隨著無線通信和射頻系統(tǒng)性能需求的不斷提高,數(shù)字預(yù)失真(DPD)技術(shù)已成為提升功率放大器線性度和效率的關(guān)鍵手段。ADRF6821 作為一款面向通信數(shù)字預(yù)失真接收系統(tǒng)的高集成度射頻集成電路,創(chuàng)新性地將分?jǐn)?shù)分頻鎖相環(huán)和多路壓控振蕩器融入同一芯片,并提供寬帶輸入覆蓋 450 MHz 到 2800 MHz 頻段。本文將從器件背景、功能特性、內(nèi)部架構(gòu)、性能指標(biāo)、典型應(yīng)用以及設(shè)計指南等多維度,對 ADRF6821 進(jìn)行系統(tǒng)而深入的介紹,以期為射頻系統(tǒng)設(shè)計工程師提供實(shí)用參考。

產(chǎn)品詳情

ADRF6821 是一種高度集成的雙射頻 (RF) 輸入、零中頻 (IF)/低 IF RFIC 接收器,具有正交解調(diào)器、數(shù)字步進(jìn)衰減器 (DSA)、IF 線性放大器、集成式小數(shù)分頻鎖相環(huán) (PLL) 和低相位噪聲多核壓控振蕩器 (VCO)。RFIC 非常適合數(shù)字預(yù)失真 (DPD) 系統(tǒng)通信。

ADRF6821 配有高度隔離的 2:1 RF 開關(guān)和片內(nèi)寬帶 RF balun,支持兩個單端 50 Ω 終止 RF 輸入。可編程衰減器確保高線性度解調(diào)器內(nèi)核具有優(yōu)質(zhì)的差分 RF 輸入電平。集成衰減器提供 15 dB 的衰減范圍,步進(jìn)大小為 1 dB。高線性度 IF 放大器跟在解調(diào)器之后,為鏈中的下一元件 — 通常是模數(shù)轉(zhuǎn)換器 (ADC) — 提供接口。

ADRF6821 提供兩種生成差分本地振蕩器 (LO) 輸入信號的方法:通過具有低相位噪聲 VCO 的片內(nèi)小數(shù)分頻頻率合成器在內(nèi)部生成,或通過相位噪聲 LO 信號在外部生成。集成合成器的連續(xù) LO 覆蓋范圍為 450 MHz 到 2800 MHz。PLL 基準(zhǔn)輸入支持頻率范圍寬廣,并且在相位頻率檢測器 (PFD) 之前有一個集成的基準(zhǔn)分頻器。

選擇之后,內(nèi)部小數(shù)分頻頻率合成器的輸出由正交相位分路器分成 2 部分。從外部 LO 路徑生成時,2× LO 信號可由正交相位分路器分成 2 部分,以生成混頻器的正交 LO 輸入。

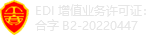

ADRF6821 通過高級硅鍺 (SiGe)、雙極互補(bǔ)金屬氧化物半導(dǎo)體 (BiCMOS) 工藝制成,采用符合 RoHS 的 56 引腳、8 mm × 8 mm LFCSP 封裝以及裸焊盤。性能是在 ?40°C 至 +105°C 溫度范圍內(nèi)標(biāo)稱。

應(yīng)用

蜂窩 W-CDMA/GSM/LTE

DPD 接收器

微波點(diǎn)對點(diǎn)無線電

特性

具有集成式小數(shù)分頻 PLL 的 DPD 接收器

RF 輸入頻率范圍:450 MHz 到 2800 MHz

內(nèi)部 LO 輸入頻率范圍:450 MHz 到 2800 MHz

雙 RF 輸入具有 SPDT 吸收式 RF 開關(guān)

集成式 RF balun 適用于單端 50 Ω 輸入

集成式 VCO 可覆蓋整個 RF 輸入范圍

數(shù)字可編程 LO 相位偏移和 dc 調(diào)零

可通過 4 線 SPI 編程

56 引腳 8 mm × 8 mm LFCSP

第二章:產(chǎn)品概述

ADRF6821 是一款高性能、寬帶射頻零中頻/低中頻接收 RFIC,集成了雙路射頻輸入、四相檢波解調(diào)、數(shù)字步進(jìn)衰減、IF 線性放大、分?jǐn)?shù)分頻鎖相環(huán)和多核壓控振蕩器。該器件采用先進(jìn)的硅鍺 BiCMOS 工藝,支持 –40°C 至 +105°C 的寬溫度范圍,封裝形式為 56 引腳、8 mm × 8 mm 的 LFCSP,便于在有限面積內(nèi)實(shí)現(xiàn)高密度射頻前端設(shè)計。

第三章:器件基本架構(gòu)

ADRF6821 的整體架構(gòu)可分為五大模塊:

射頻輸入與開關(guān)模塊:采用集成式 2:1 吸收型 RF 開關(guān),支持兩路單端 50 Ω 終端射頻輸入;

射頻變壓器與移頻解調(diào)模塊:內(nèi)部寬帶 RF 平衡至差分變壓器,后接四相檢波混頻器,可實(shí)現(xiàn)零中頻或低中頻輸出;

數(shù)字步進(jìn)衰減模塊:提供最多 15 dB 的衰減范圍,步長 1 dB,確保進(jìn)入解調(diào)器的差分信號電平在最佳線性范圍;

中頻放大與濾波模塊:高線性 IF 放大器結(jié)合可編程低通濾波,為后續(xù) ADC 或數(shù)字解調(diào)提供平衡驅(qū)動;

本振信號源與鎖相環(huán)模塊:內(nèi)置分?jǐn)?shù)分頻鎖相環(huán)及多核壓控振蕩器,覆蓋 450 MHz 至 2800 MHz 的 LO 生成,或接受外部 LO 驅(qū)動。

第四章:集成式分?jǐn)?shù)分頻鎖相環(huán)

ADRF6821 內(nèi)部的分?jǐn)?shù)分頻鎖相環(huán)(PLL)由相位頻率檢測器(PFD)、電荷泵、環(huán)路濾波器網(wǎng)絡(luò)以及分頻模/分頻器構(gòu)成。其核心優(yōu)勢在于:

大范圍的參考頻率支持,使設(shè)計者能夠靈活選擇晶振或外部參考;

精細(xì)的分?jǐn)?shù)分頻控制,實(shí)現(xiàn) LO 頻率微調(diào),滿足現(xiàn)代蜂窩通信中對頻率精度和相位噪聲的嚴(yán)格需求;

內(nèi)置可編程參考分頻器和反饋分頻器,降低外部元件數(shù)量與系統(tǒng)布局復(fù)雜度。

第五章:多核壓控振蕩器(VCO)

VCO 模塊采用多核設(shè)計,以覆蓋從 450 MHz 到 2800 MHz 的射頻輸入范圍,并提供 2 倍倍頻輸出能力至 900 MHz 至 5600 MHz。本振輸出的性能指標(biāo)包括:

低相位噪聲:在成品設(shè)計中可滿足 < –110 dBc/Hz @ 1 MHz 偏移的要求;

寬頻帶調(diào)諧:通過調(diào)諧電壓 VTUNE 可實(shí)現(xiàn)連續(xù)頻率覆蓋;

穩(wěn)定性與溫度補(bǔ)償:工藝和電路設(shè)計保證在寬溫度范圍內(nèi)保持頻率穩(wěn)定,減小溫漂。

第六章:數(shù)字預(yù)失真(DPD)功能

ADRF6821 專為與數(shù)字預(yù)失真處理器配合使用而設(shè)計,其高線性解調(diào)和寬帶 IF 驅(qū)動能力,為 DPD 算法在基帶數(shù)字信號處理器中提供精確采樣和誤差反饋。主要特點(diǎn)包括:

零中頻或低中頻輸出靈活選擇,兼容多種 DPD 架構(gòu);

較高的輸入 1 dB 壓縮點(diǎn)(IP1dB > +10 dBm),確保接收鏈在高功率下仍具備優(yōu)秀線性;

可編程 DC 偏置和相位偏移校正,通過 SPI 接口快速配置,以配合不同放大器的特性。

第七章:射頻輸入與開關(guān)設(shè)計

器件內(nèi)置的集成射頻開關(guān)具備高隔離度和低插入損耗,實(shí)現(xiàn)雙通道射頻切換而無需外部開關(guān)。設(shè)計要點(diǎn)如下:

射頻輸入必須 AC 耦合,確保 DC 偏置分離;

外部 50 Ω 匹配網(wǎng)絡(luò)設(shè)計可根據(jù)實(shí)際板級布局進(jìn)行微調(diào);

推薦在輸入采樣處添加微帶濾波,抑制帶外干擾并改善信號純凈度。

第八章:中頻放大與輸出接口

中頻輸出部分包括平衡差分放大器和可編程低通濾波器,可配置帶寬高達(dá) 500 MHz。

差分輸出驅(qū)動 ADC:為下一級 ADC 或數(shù)字解調(diào)芯片直接提供低阻抗差分信號;

帶寬與增益可通過寄存器設(shè)置:設(shè)計者可依據(jù)系統(tǒng)帶寬需求和信號功率級別靈活配置。

第九章:寄存器編程與數(shù)字接口

ADRF6821 通過四線串行外設(shè)接口(SPI)進(jìn)行寄存器編程,主要包括:

時鐘信號 SCLK、數(shù)據(jù)輸入 SDIO、數(shù)據(jù)輸出 SDO 與片選 CS;

10 位或 14 位可編程寄存器,用于配置 PLL 分頻比、衰減值、相位偏移、DC 校正等;

軟件提供 ACE(Analysis Control Evaluation)工具,支持圖形化配置與快速評估。

第十章:性能指標(biāo)

在典型工作條件下,ADRF6821 主要性能參數(shù)如下:

射頻輸入范圍:450 MHz 至 2800 MHz;

本振輸出范圍:900 MHz 至 5600 MHz;

相位噪聲:–110 dBc/Hz @ 1 MHz 偏移(典型);

1 dB 壓縮點(diǎn):+10 dBm(RF 輸入);

互調(diào)失真(IMD3):< –70 dBc;

工作電壓:3.3 V 核心電源,5.6 V 推薦電源;

功耗:典型 600 mW。

第十一章:典型應(yīng)用場景

ADRF6821 廣泛應(yīng)用于:

蜂窩基站和室內(nèi)分布系統(tǒng)(DAS)中的數(shù)字預(yù)失真接收模塊;

微波點(diǎn)對點(diǎn)無線電鏈路;

多模多頻無線寬帶接入設(shè)備(WiMAX、LTE、5G NR 異構(gòu)網(wǎng)絡(luò));

測試與測量儀器中的寬帶信號分析前端。

第十二章:PCB 布局與電路設(shè)計注意事項

為了充分發(fā)揮 ADRF6821 的性能,版圖設(shè)計需關(guān)注:

電源去耦:在各電源管腳附近放置低 ESR 陶瓷電容和阻抗匹配良好的地平面;

射頻路徑:使用 50 Ω 微帶線或帶狀線,避免信號轉(zhuǎn)角和不必要的 vias;

接地:射頻地與數(shù)字地分區(qū),并在適當(dāng)位置進(jìn)行匝間連接,減少環(huán)路面積;

溫度管理:在高功率環(huán)境下,需考慮 PCB 散熱、熱過孔分布與散熱銅皮設(shè)計。

第十三章:FPGA 與 ADC 接口設(shè)計

結(jié)合 FPGA 或?qū)S?DPD 處理器,設(shè)計者需:

確保 IF 信號帶寬匹配 ADC 采樣率;

在 ADC 前加入抗混疊濾波;

在 FPGA 中實(shí)現(xiàn)高精度定時與相位校正,利用 ADRF6821 提供的相位偏移和 DC 校正功能,簡化數(shù)字校準(zhǔn)算法。

第十四章:評估板(EVAL-Z)介紹

ADRF6821-EVALZ 評估板提供即插即用功能:

集成 SDP?S 控制接口,可通過 ACE 軟件實(shí)現(xiàn)一鍵配置;

5.6 V 單電源供電,板載 LDO 提供 3.3 V,兼容實(shí)驗(yàn)室環(huán)境;

SMA 射頻連接器與分立元件布局,使工程師快速驗(yàn)證器件性能并優(yōu)化系統(tǒng)。

第十五章:未來發(fā)展與趨勢

隨著 5G NR、毫米波通信和大規(guī)模天線陣列技術(shù)演進(jìn),射頻前端將向更高帶寬、更低功耗和更智能化方向發(fā)展。ADRF6821 代表了集成分立元件向高集成度 RFIC 的趨勢。在未來,還可通過:

增加 PLL 數(shù)字化控制精度;

引入更先進(jìn)的 GaN 或 SiGe 工藝以提升線性;

將更多射頻前端功能集成于同一芯片,實(shí)現(xiàn)更小尺寸和更高密度的基站設(shè)備。

第十六章:總結(jié)

ADRF6821 以其寬頻覆蓋、低相位噪聲、高線性和高集成度,為通信 DPD 接收系統(tǒng)提供了理想的解決方案。通過深入了解其架構(gòu)、功能和設(shè)計要點(diǎn),系統(tǒng)工程師可在射頻前端設(shè)計中最大化性能,提升無線通信系統(tǒng)效率與穩(wěn)定性。無論是在蜂窩基站、寬帶接入還是專業(yè)測試設(shè)備中,ADRF6821 均展現(xiàn)出廣闊的應(yīng)用前景。

產(chǎn)品分類

產(chǎn)品分類

2012- 2022 拍明芯城ICZOOM.com 版權(quán)所有 客服熱線:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版權(quán)所有 客服熱線:400-693-8369 (9:00-18:00)